# A NEW PROBABILISTIC APPROACH TO VLSI CIRCUITS TESTING\*

M.C. Karpovsky and L.B. Levitin College of Engineering Boston University Boston, MA, USA

## 1. Introduction

It is well known that the problem of test generation becomes intractable (NP-hard) for complex circuits (with large numbers of inputs, gates and connecting lines), if one tries to find an optimal specific test for any given circuit.[1,2] Even to construct a test which is not optimal, but provides a good fault coverage (say, > 95%) is quite difficult. It results usually in an excessively large size of a test (in some cases the tests include tens of thousands of test patterns). Test generation and application become more and more time - and money - consuming and threaten to turn into a real bottleneck of the computer industry. The time and the cost of testing increases tremendously (in general, exponentially) with the complexity of the devices to be tested. The cost of testing is already, in many cases, higher than the cost of development and manufacturing. 'The majority of direct labor time required to

<sup>\*</sup>This work was partially supported by the National Science Foundation under Grant MCS8021262.

build an Apple III is straight test time.....Testing requires 35% of the direct labor time involved in building a system.....If the test and the rework time is added together, 72% of the process time is accounted for.'[3] There is a common understanding among specialists that efforts must be concentrated to fight this trend: 'It has become evident to designers and test engineers that to combine development of VLSI, new techniques tackling the problems of testing parts are needed over and above mere extensions.'[4]

The following three approaches have been traditionally used for testing, namely: gate-level testing, functional testing and random testing. For the gate-level testing the input data for test generation consist of a gate-level description of a device under test and a gate-level description of a class of possible faults. This approach has been proved to be very efficient for SSI and MSI circuits, [5,6,7]. The classical D-algorithm [6] has been widely used for gate-level testing during many years. With the transition to VLSI technology the gate-level description of a device under test becomes too complicated and in many cases (in particular, for the user) is not available at all. Even if the gate-level description is available to a test designer the cost of test generation in many cases begins to be prohibitively high for VLSI devices [8].

These considerations stimulated the development of functional testing approach, especially for microprocessors testing. In the case of functional testing, the input data for

testing is represented by a functional description of a device under test and of a class of faults [9,10,11,12,13,14,15]. In [9,10] the functional testing approach has been used for testing of microprocessors in a user's environment. This procedure was based on a general graph-theoretical model of a microprocessor at the register-transfer level. The functional fault model was developed using the register-transfer level description and the instruction set.

Binary decision diagrams have been used for functional testing in [11], where this approach has been applied to testing of ALU. For functional testing the cost of test generation for VLSI devices is still very high, especially when a broad spectrum of devices has to be tested. On the other hand, it is very difficult, in general, to estimate fault coverage in the case of functional testing.

For random testing test patterns are generated randomly [16,17,18,19,20,21,22,23,24,25]. For generation of pseudorandom test patterns linear feedback shift registers has been used [26]. Random testing has been used both at the gate level and at the functional level. In the latter case a random sequence of instructions has been used for testing (see,e.g., [24]). The major problem in random testing is to estimate the test length and the probability of fault detection [23,24]. For random testing the cost of test generation is not high but a number of test patterns (testing time) may be very high for VLSI devices.

There is one more approach for testing, when one does not

deterministic standard test which can be used for a large set of devices. One example of this approach is presented in [27] where exhaustive testing and simple data compression schemes have been used for testing. In [28,29,30] standard tests have been developed for combinational devices such that every output depends only on a small subset of inputs.

## 2. The Concept of Universal Testing

Tortunately, the same reasons that make the problem of generation of individual test for various VLSI circuits so difficult - namely, the increasing complexity and large diversity of the circuits - open a way to a different approach to test This approach has been recently developed in generation. [31,32,33,34], and called <u>universal testing</u>. To explain the basic idea of this new approach we need to turn from the deterministic concept of testing to the probabilistic one. It is somewhat similar in 'ideology' to the transition from mechanics to statistical mechanics. Indeed, it is well known that only very simple mechanical systems can be treated in a deterministic way (the famous 'three-body problem' of celestial mechanics has no general solution). On the other hand, when the number of particles (or degrees of freedom) of a system becomes very large, the methods of statistical mechanics can be applied. Statistical mechanics describes the behavior of a large ensemble of systems of a given kind, rather than the details of the trajectory of an

individual system. The remarkable fact is that the larger is the system the more exactly the vast majority of all such systems follows the same typical pattern of behavior, so that the probability that an individual system will deviate considerably is vanishingly small. Thus, the laws of statistical mechanics (thermodynamics), though being probabilistic in nature, become fully deterministic for all practical purposes. The major breakthrough in communication engineering owing to Shannon's informations theory was based on very similar ideas [35,36,37,38]. The same philosophy was successfully applied in some other areas, such as collective behavior of automata [39,40], neural networks [41], etc.

This way of reasoning brings us to the idea of universal tests - the tests that are able to detect all the faults of a given class in almost all circuits of a given ensemble of circuits. The fraction of the circuits in which a universal test detects all the faults of a given class approaches one when the circuit complexity increases. The rigorous definition of universal sequence of tests is given in Sec. 3. Preliminarily, the concept of universal testing can be explained in the following way. Let  $C_i = \{c_{ij}\}$  be a finite set of circuits  $c_{ij}$  of a given complexity, the complexity increasing with i. Suppose that a circuit  $c_{ij}$  can be chosen randomly from the set  $C_i$  with probability  $P_{ij}$  ( $\sum_{j} P_{ij} = 1$ ). Denote by  $F_i$  a set of faults of given type F which can occur in any  $c_{ij}$ . Denote by  $P(T_i, F_i, C_i)$  the probability that the test  $T_i$  detects all the errors from  $F_i$

in a circuit cij randomly chosen from Ci with probability Pijo Def. 1. A sequence of tests (Ti) is called universal for detection of all faults of type F if

$$\lim_{i \to \infty} P(T_i, F_i, C_i) = 1$$

(1)

To avoid misunderstanding, we would like to stress that the probability P is the fraction of the circuits for which the universal test provides complete (100%) fault coverage (and not the measure of fault coverage for a given circuit).

testing on one hand, and universal tests, on the other as the latter term is used in [42, 43]. Our approach is essentially probabilistic, and the universality is understood in the asymptotic meaning, as expressed in Def. 1. No use of additional hardware and no special design is assumed to improve testability of the circuits. The authors of [42, 43] suggest tests which can detect some classes of faults in all PLA with given numbers of inputs and product terms (in a deterministic way), but they can do it only by the expense of adding extra logic and designing the PLA's in a special way. Thus the interesting approach adopted in [42, 43], belongs, in essence, to the 'design for testability' area, and differs in principle from our approach.

One should not confuse universal testing with another probabilistic approach - random testing. The comparison of gate-level testing, functional testing, random testing and universal

testing is given in Sec. 5 of this paper. Universal tests are somewhat similar to standard tests and aimed to fill the gap between the functional and random testing, combining the advantages of both of them. For universal testing the input data for test generation consists of parameters of a device under test (e.g., numbers of input and output lines, numbers of flip-flop, etc.) and description of a class of possible faults (e.g., stuck-at faults of a given multiplicity). Universal tests may be very efficient for a testing of a broad spectrum of devices or as a first step in a testing procedure.

The use of the concept of 'almost all devices' needs some justification. Indeed, it implies that universal testing methods divide a given set of circuits into two subsets: circuits in which all the faults of a given class are detectable by the test (let us call them 'sheeps'), and those which are not completely testable ('goats'). It might happen that, though the latter ones constitute only an infinitesimally small fraction of the total set, practically we are dealing just with these 'exceptional', 'non-typical' circuits. In fact, a similar situation is not at all unusual in coding theory, logic design, etc. (One may call it 'Shannon paradox', since it appears, in particular, in information theory). To illustrate this point, let us consider a relevant example from the theory of complexity of Boolean functions.

It is well known that for almost all Boolean functions of marguments, the minimal number G(m) of two-input gates in network

implementing these functions is  $G(m) \sim \frac{x \cdot 2^m}{m}$  (r is a constant) [44], but not even one class of Boolean functions which require for their implementation more than a polynomial number of gates is known yet.

The second example relates to Shannon's basic coding theorem which states that almost all block codes of a given length provide data transmission rate arbitrarily close to the channel capacity with probability of error tending to zero when the length increases. But in spite of the fact that all but infinitesimal small fraction of codes are 'good', not a single class of such codes was known until quite recently [45].

Fortunately, this is not the case in universal testing. A number of examples considered below will demonstrate applicability of universal testing to some practically important classes of circuits. Though examples of 'goats' can be indicated among practical circuits, they seem to be relatively rare.

Universal tests for terminal stuck-at and bridging faults in combinational circuits have been developed in [31-34]. Consider the standard combinational circuits regarding their testability by these universal tests. A circuit is called a 'sheep' (s), if universal tests provide 100% coverage of faults of a given class, and it is called a 'goat' (g) otherwise. The classification is given in Table 1. One can see that 'sheeps' with respect to one class of faults may be 'goats' with respect to another class.

Table 1 Testability of standard computer components by universal tests  $(m \rightarrow \infty)$ . s - 'sheeps', g - 'goats'

| Name of the Circuit                                       | CLASS OF FAULTS   |                    |  |

|-----------------------------------------------------------|-------------------|--------------------|--|

| ·                                                         | Input<br>Stuck-at | Input<br>Bridgings |  |

| AND, OR, NAND, NOR gates                                  |                   |                    |  |

| arity checker                                             | g                 | •                  |  |

| (ajority gate (m=2-)                                      | <b>\$</b>         | •                  |  |

| hifter (with 2 control                                    | g                 | •                  |  |

| inputs)                                                   | 8                 | •                  |  |

| Ode convertors (binary to BCD, binary to Grey code, etc.) | <b>\$</b>         | *                  |  |

| unter with parallel load<br>-and-down counter<br>der      | . <b>.</b>        | <b>5</b>           |  |

| nbtractor                                                 |                   | \$                 |  |

| ultiplier                                                 | £                 | 5                  |  |

| ecoder                                                    | g                 | *                  |  |

|                                                           | -                 | \$                 |  |

| ultiplezer                                                | •                 | 8                  |  |

| •                                                         | <b>B</b>          | 8                  |  |

It is remarkable that while elementary AND, OR, NAND and NOR are 'goats', more complex circuits become 'sheeps'.

Since universal testing of combinational circuits was the object of [31-34], in the present paper we shall consider mostly results related to sequential circuits.

## 3. Definitions and Notations.

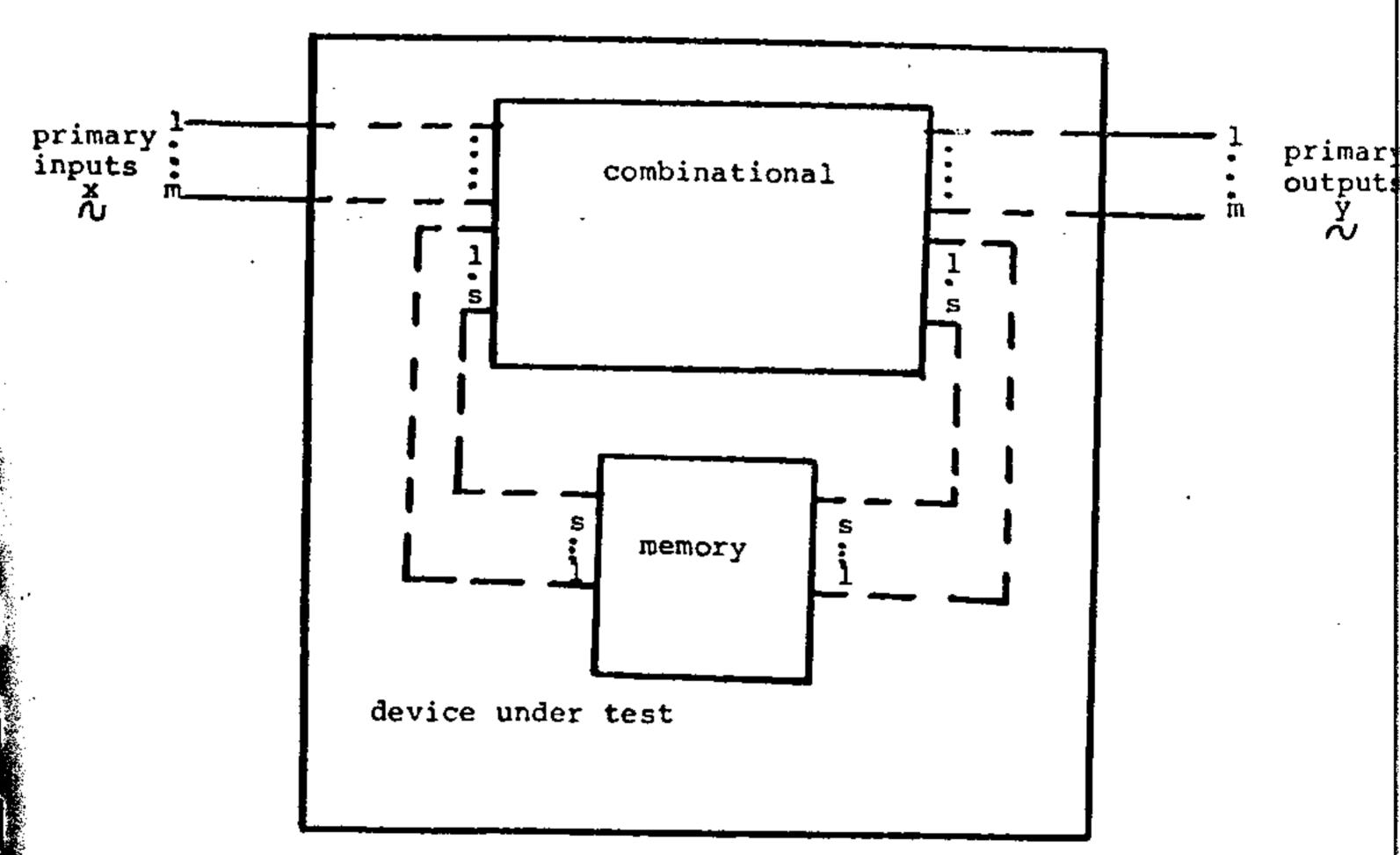

An arbitrary digital binary circuit with memory may be represented by a block-diagram of Fig. 1.

Here m is the number of input lines, k is the number of output lines, and s is the number of feedback lines (the number of binary memory cells). Such a device will be referred to as an (m,k,s) - circuit so that an (m,k,o) - circuit is a combinational circuit.

#### Denote also:

$= (x_1, \dots, x_m)$  is an input binary vector,

$\sum_{k=0}^{\infty} (y_1, \dots, y_k)$  is an output binary vector,

$z = (z_1, \dots, z_s)$  is a feedback binary vector.

For a given circuit c at discrete time v:

$y_{j}(\tau) = y_{j}^{c}(z(\tau), z(\tau-1)), j=1,...,k,$

$z_r(\tau) = z_r^c(x(\tau), z(\tau-1)), r=1,...,s,$

(2)

where  $y_1^c$  and  $z_1^c$  are Boolean functions of (m+s) variables, which are specified by the structure of the circuit c. A test  $T^{(m,N)} = (t_1^{(1)}, \ldots, t_n^{(N)})$  is a sequence of N binary m - dimensional vectors  $t^{(g)} = (t_1^{(g)}, \ldots, t_m^{(g)})$ ,  $g=1, \ldots, N$ , which are applied to the input lines of the circuit. In the absence of input faults, obviously,  $x^{(g)} = t^{(g)}$ .

We denote by  $Y^{(k,N)}=(y^{(1)},\ldots,y^{(N)})$  the sequence of output vectors produced by application to the circuit a sequence of test patterns  $T^{(m,N)}=(t^{(1)},\ldots,t^{(N)})$ , provided that the memory was cleared before testing. For a fault-free device Y(k,N) is

Fig. 1. Block-diagram of a device with memory.

uniquely determined by  $T^{(m,N)}$ . However, if a fault foccurs in the circuit,  $Y^{(k,N)}$  may depend on the fault:  $Y^{(k,N)}=Y^{(k,N)}(f)$ . Denote by for the situation when circuit c is fault-free.

Definition 2. It is said that test  $T=T^{(m,N)}$  detects a fault f in a given circuit c, if for this circuit

$$Y(k,N)(f) \neq Y(k,N)(f_0).$$

(3)

Consider now a set of faults  $F=\{f_w\}$ ,  $w=0,1,\ldots$ , w, w=|F|-1, which may occur in the circuit c.

Definition 3. It is said that test  $T=T^{(m,N)}$  detects all the faults from set F in the circuit c if for any  $f_{\psi} \in F$ ,  $\psi \neq 0$ ,

$$Y^{(k,N)}(f_w) \neq Y^{(k,N)}(f_o)$$

(4)

Definition 4. It is said that test  $T=T^{(m,N)}$  identifies all the faults from set F in the circuit c if for any  $f_v$ ,  $f_w \in F$ ,  $v \neq w$ ,

$$Y^{(k,N)}(f_{\nabla}) \neq Y^{(k,N)}(f_{\nabla}) \qquad (5)$$

Now let us consider a set of circuits  $c=\{c_n\}$ ,  $n=1,\ldots,M$ , and a probability space (E,B,P), where E is the space of elementary events  $E=\{e_n\}$ , the elementary event  $e_n$  is the application of a given test T to the circuit  $c_n$ , B is a Borel field on E, and P is a probability measure on E, defined by the probabilities of elementary events  $p(e_n)$ . For a given set of faults F there exists an element  $B_{det}(F)$  (respectively  $B_{id}(F)$ ) of the Borel field B which is the set of all the elementary events  $e_n$  such that (4) (respectively, (5)) is satisfied for the circuit  $c_n$ .

Then the corresponding probabilities

$$P\{B_{det}(F)\} = \sum_{p(e_n)}.$$

(6)

$$e_n \epsilon B_{det}(F)$$

$$P\{B_{id}(F)\} = \sum_{p(e_n)} (7)$$

$$e_n \epsilon B_{id}(F)$$

have a meaning of probabilities that the test T detects (respectively, identifies) all the faults from set F being applied to a circuit chosen randomly from c according to probability distribution  $p(e_n)$ . Henceforth we shall assume that  $c = c_{seq}$  is the set of all possible (m,k,s) - circuits, i.e., each circuit  $c_{ns}C_{seq}$  is a relaization of (k+s) (not necessarily distinct) Boolean functions of (m+s) input variables, and exactly one circuit corresponds to any possible ordered (k+s)-tuple of Boolean functions. Thus,  $|C_{seq}| = |K| = 2^{(k+s)}2^{m+s}$ . We assume also that the probability distribution is uniform:  $p(e_n) = \frac{1}{K}$ . Then  $P\{B_{det}(F)\} = P_{det}(T, F, m, k, s,)$  and  $P\{B_{id}(F)\} = P_{id}(T, F, m, k, s)$  are equal to the fractions of all the (m,k,s) - circuits in which test T detects (respectivley, identifies) all the faults from set F.

Now let m be a (natural) variable, and k and s be functions of m (in particular, constants). Consider a sequence of sets  $(C_{seq}=C(m,k,s))$  where m takes on increasing natural values, and a sequence of corresponding tests  $(T^{(m,N)})$ , where N is a function of m.

Definition 5. A sequence of tests  $(T^{(m,N)})$  is called universal

for detection (respectively, for identification) of all faults from set F = F(m,k,s), if

$$\lim_{m\to\infty} P_{\det}(T,F,m,k,s)=1$$

(8)

instead of "universal sequence of tests"). It is seen from Definition 5, that the performance of universal tests becomes the better, the larger are VLSI devices under test. This asymptotic property of universal tests makes this approach especially relevant for complex VLSI circuits.

The following notations will be used throughout the paper: ! - multiplicity of faults.

$\hat{T}$  - test matrix formed by test patterns from T as rows.

$N_{det}(F,m,k,s)$   $(N_{id}(F,m,k,s))$  - asymptotic minimum number of test patterns in universal tests for detection (respectively, identification) of all fault from F.

$\varepsilon(a)$  - an arbitrary function such that  $\varepsilon(a) \rightarrow \infty$  when  $a \rightarrow \infty$ .

Two different constructions of universal sequence of tests will be used. In the first sequence the test of size N has the following structure:

$$t_i^{(1)} = 0$$

,  $i = 1, ..., m$ ;

$t_h^{(2h+1)} = 1$ ,  $t_i^{(2h+1)} = 0$ ,  $i \neq h$ ,  $i = 1, ..., m$ ,  $h = 1, ..., \frac{N}{2} - 1$ ; (10)

$t_h^{(2h)} = t_h^{(2h-1)}$ ,  $h = 1, ..., \frac{N}{2}$ .

Here E is a binary vector which is the complement (negation) of I. Note that the order of test patterns (indicated by the upper index) is essential in the case of networks with memory.

The second construction makes use of Hadamard matrices. Let n be the minimum number such that  $n \ge m$  and there exists a binary Hadamard matrix  $\widehat{A}_n$  of order n [44]. We use the conjecture (proved for all n\langle 268) that a Hadamard matrix exists for all n which are multiples of 4. Consider an  $(n \times m)$ -matrix  $\widehat{A}$  whose columns coincide with the first m columns of  $\widehat{A}_n$ . Let  $a_h$ ,  $h=1,2,\ldots,n$  be the h-th row of the matrix  $\widehat{A}$ . Design a test  $T=T^{(m,N)}$  as follows:  $t^{(1)}=0$ ,  $t^{(2)}=t^{(1)}$ ,  $t^{(2g+1)}=a_g$ ,  $t^{(2g+2)}=t^{(2g+1)}(g=1,2,\ldots,\frac{N}{2}-1)$ , where  $N=|T|\le 2n$  and Q denotes all zeros vector.

## 4. Applications of universal tests to sequential circulits.

## 4.1. Detection of input stuck-at faults.

Universal testing of terminal faults in sequential circuits is a natural generalization of the approach applied to the terminal faults in combinational circuits in [31-34]. Yet it poses a number of quite non-trivial new problems, since the temporal behavior of sequential circuits is much more complex. In particular, the time order of test patern becomes essential in this case. We present here results related to single input stuck-at faults in (m,k,s) - circuits.

Denote by  $F_1^{(st)}$  the set of all single input stuck-at faults.

Theorem 1. (i). The probability that a test T=T(m,N) defined by (10) detects all the faults from  $F_1^{(st)}$  in a circuit chosen by random from  $C_{seq}$  satisfies the inequality:

$$P(T,F_1^{(s+t)},C_{seq}) \geq [1-2^{\frac{-KN}{2}}(2^{-s}+(1-2^{-s})2^{-k})^{\frac{N}{2}}]^{2m}.$$

(12)

(ii). The tests defined by (10) form a universal sequence of tests for detection of all the faults from  $F_1$  (5t), if

$$N = 2 \frac{\log_{2} m + \epsilon(m)}{k - \log_{2}(2^{-S} + (1 - 2^{-S})2^{-K})}$$

(13)

(iii). The minimum number of test patterns in a universal sequence of test which detects all the faults from  $F_1(st)$  in almost all (m,k,s) - circuits is

$$N(F_1^{(S4)}, m, k, s) \sim 2$$

$$\frac{\log_2 m}{k - \log_2 (2^{-S} + (1 - 2^{-S}) 2^{-K})}$$

(14)

Theorem 1 is a generalization of Theorem 1 and Theorem 2 in [34] for the case when the set of faults is  $F_1^{(st)}$  It can be proved by a similar technique, taking into account that for a test T(m,N) defined by (10) either  $t^{(2g-1)}$  (f) $\neq t^{(2g-1)}$ , or  $t^{(g)}$  (f) $\neq t^{(g)}$  for all  $g=1,2,...,\frac{N}{2}$ . (Here t(f) is the external input vector in the presence of fault f.)

In partcular,

$$\begin{cases}

2 \frac{\log_2 m}{k}, & \text{if } \frac{S}{K} \longrightarrow 0: \\

2 \frac{\log_2 m}{k}, & \text{otherwise.}

\end{cases}$$

(15)

Comparing (13) with the corresponding results for combinational circuits [31, 33] one can see that for a small number of memory cells numbers of test patterns for combinational and sequential circuits are symptomatically equal, but if  $s \geq k$ , then the size of the test can be reduced by half.

Example 1. Consider detection of stuck-at faults in an adder accumulator with m input lines. In this case k=s>m, and the test  $T^{(m,2)}$  with test patterns  $t_1 = 0 = (0,...,0)$ ,  $t_2 = 1 = (1,...,1)$

detects all the faults, which agrees with Theorem 1.

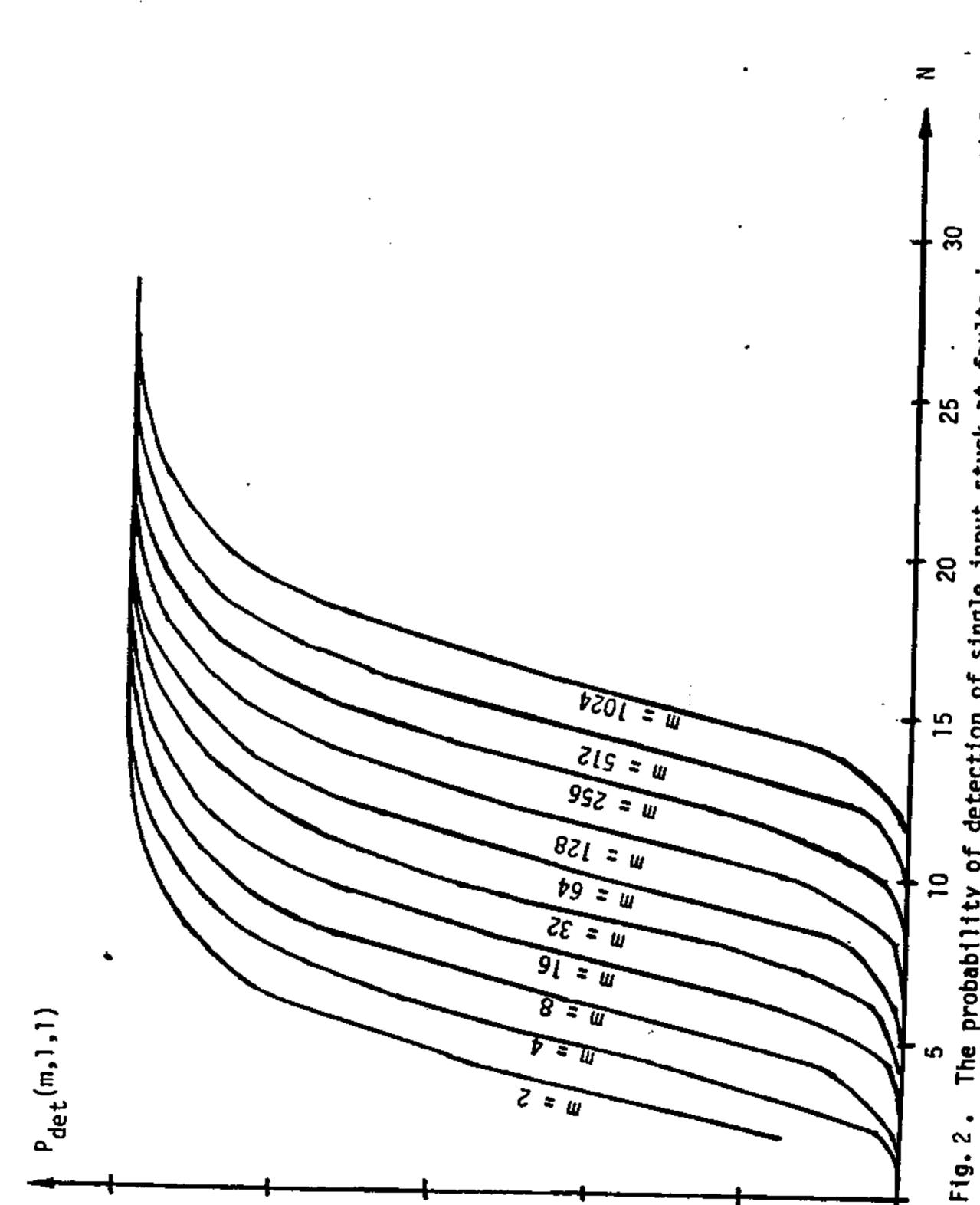

The probability  $P(T,F_1^{(st)})$ ,  $C_{seq}$  converges to 1 very fast with the increase of the number of test patterns. For example, if m=s=16, k=1, then  $P(T,F_1^{(st)})$ ,  $C_{seq}^{(st)} \geq 1-2^{-5}$  for N=10 and  $P(T,F_1(st))$ ,  $C_{seq}^{(st)} \geq 1-2^{-15}$  for N=20. Some numerical values of  $P(T,F_1(st))$ ,  $C_{seq}^{(st)} \geq 1-2^{-15}$  in Figure 2, for k=s=1.

single input stuck-at faults in sequential patterns. test o f number the The probability of detection of οf function ø a S circuits (m,1,1)-

## 4.2 Detection of stuck-at faults in memory.

Universal testing of internal faults is a complicated problem because of its generality and because the concepts of controllability and observability come into play in a more involved manner than for terminal faults. (Terminal faults can be considered as a very special case, when we have either complete controllability (input faults), or complete observability (output faults)).

We shall illustrate how universal tests can be applied to detection of internal faults by the example of the faults in memory cells in (m,k,s)-circuits. This class of faults, F (m) (lis the largest fault multiplicity), deserves special analysis, since in many practical situations memory cells are less reliable than gates. Tests defined by (11) appear to be convenient for detection of these faults. The results obtained for this class of faults are summarized in the following theorem.

Theorem 2. (i) The probability that a test defined by (11) detects all the faults from  $F_{\ell}^{(m)}$  in an (m,k,s)-circuit chosen randomly from  $C_{\text{seq}}$ , is bounded  $\ell$  by:

$$P(T, F_{\ell}^{(m)}, C_{seq}) \ge \left(1 - \left(\frac{1+2^{-k}}{2}\right)_{N}\right)^{\sum_{i=1}^{2} i \binom{s}{i}}$$

(16)

(ii) The tests defined by (11) form a universal sequence of tests for detection of all the faults from  $F_{\ell}^{(m)}$ , if

$$N = \begin{cases} \frac{1 \log_2 \sum_{i=0}^{\ell} 2^{i} {5 \choose i} + \epsilon(s) \\ \\ \frac{1 - \log_2 (1 + 2^{-K})}{} \end{cases}$$

(17)

(iii) The minimum size of tests in a universal sequence of tests for detection of all faults from  $F_{\ell(m)}$  is

$$1 \circ g_{2} \stackrel{\stackrel{P}{=}}{=} 2^{i} \binom{s}{i}$$

$$N(F_{p}^{(m)}, m, k, s) \stackrel{\checkmark}{\checkmark} \frac{1 - 1 \circ g_{2} (1 + 2^{-k})}{(18)}$$

To prove (16) we note that a fault in memory cells is not detected either if the memory output is not distorted by the fault, or if the memory output is distorted by the fault, but is "masked" by the combinational part of the circuit. The total probability of non-detection of a given fault by N test patterns does not exceed  $(1+2^{-K})^N 2^{-N}$ , which leads to (16). Then (17) and (18) can be obtained by use of the definition of universality: (17) is the necessary and sufficient condition for the convergence of  $P(T,F_{\underline{f}}^{(m)},C_{seq})$  to 1.

In particular, for detection of single stuck-at faults in memory

$$P(T,F_1^{(m)},C_{seq}) \ge [1-(1+2^{-K})^N 2^{-N}]^{2S}$$

, (19)

and for detection of all possible memory stuck-at faults (l=s)

$$P(T,F_{s}^{(m)},C_{seq}) \ge [1-(1+2^{-K})^{N} 2^{-N}]^{3^{s}-1}$$

(20)

For example, if k=s=16,  $P(T,F_1^{(m)},C_{seq}) \ge 1-2^{-15}$  for N=20, and  $P(T,F_s^{(m)},C_{seq}) \ge 1-2^{-15}$  for N=40.

The number of test patterns for l=s

$$N(F_{s}^{(m)}, m, k, s) \le s(1-\log_2(1+2^{-K})) \log_2 3$$

(21)

Thus, the number of test patterns grows at most linearly with the number of memory cells.

It can be shown that identification of input stuck-at faults and memory faults in (m,k,s) - circuits requires universal tests of double size as compared with universal tests for detection of those faults (i.e.  $N_{id}(F,m,k,s) = 2N(F,m,k,s)$ ).

# 5. Advantages and Limitations of Universal Testing Methods. General remarks.

As any other method of testing, universal tests have their specific advantages and limitations. In this section we discuss briefly some general properties of universal tests, and then we compare this approach with other known methods.

## 5.1. Advantages.

- 1. Simple test generation. Since universal tests are developed for a wide class of circuits, it eliminates the necessity of generating tests individually for any particular device the problem that becomes practically unsolvable for complex circuits, if we want to test them on the gate level.

- 2. Guaranteed full coverage for almost all devices. The estimation of fault coverage poses sometimes a difficult problem, for instance, in functional testing. Universal tests are constructed in such a way as to provide a 100% coverage of faults for almost all devices from a broad set. It should be taken into account, however, that this coverage is provided for a specific class of faults, for which this particular universal test was designed.

- 3. Applicability to complex circuits. The crucial question in universal testing is, of course, how large is the fraction of 'goats' the circuits which are not completely testable by a given universal test. Perhaps, the most attractive feature of universal tests is that they are asymptotically efficient, i.e., they work the better the more complex is the circuit under test (e.g., the larger is the number of input and/or output faults). Therefore universal testing seems to have a good potential for VLSI testing.

For example, consider universal testing of input stuck-at faults of multiplicity at most k (set of faults  $F_k$  ) in combinational (m,k,o)- circuits. This problem has been solved in

[33,34]. The results show that if the size of the test is chosen in such a way that  $N = N(F_{\ell}^{(5t)}, m, k)$  (1+8) and  $\lim_{m \to \infty} \frac{\ell}{m} = 0$ , then

the fraction of "goats" approaches zero as  $m^{-\ell\delta}$  when  $m \longrightarrow \infty$ . Notice also that it works the better the larger is the multiplicity of faults  $\ell$ . (Of course, the corresponding test size is also larger). For single stuck-at faults (the worst case) and  $\delta = 5$ ,  $m = 15 \div 20$ , the fraction of "goats" does not exceed 1%.

- 4. Easy extension. Sometimes we may be interested to extend the universal test in order to further diminish the risk to encounter a "goat". The universal tests designed above can be easily extended (up to the limit N = 2m) without any change in construction. As it was shown above, with the increase of the number of test patterns, the probability that the device under test is a "goat" decreases exponentially.

- 5. Good coverage for "goats". One should not think that the "goats" are tested poorly by universal tests. The situation is just the opposite: in fact, though the coverage of faults in "goats" is not complete, almost all "goats" are covered almost completely. For example, if total fraction of "goats" is 1%, then only in 0.5%

of them (i.e., in a 5.10°5 fraction of all the circuits) two or more faults remain undetected, and only in a 1.7×10°7 fraction of all the devices more than two faults are undetectable by the test.

Let us comsider now the general case when the required

coverage of faults is not 1, but  $1-\beta\langle 1$ . It has been recently

shown ([34], Theorem 7) that in order to detect a fraction of (1- $\beta$ ) W faults (out of the total number W) in almost all circuits the minimum number of test patterns in a universal sequence of tests obeys inequalities:

$$N^{(\beta)}(F_{\underline{l}}^{(st)}, \mathbf{n}, \mathbf{k}) \leq 2\left(\frac{1-\log_2\beta}{K}\right)$$

(22)

for input stuck-at faults of any multiplicity &, when m->o, and

$$N^{(\beta)}(F_{\ell}^{(st)}, m, k) \leq n(m, \lfloor \frac{1-\log_2\beta}{K} \rfloor)$$

(23)

for any input bridgings,  $m \to \infty$ , where n(m,d) is the length of a shortest linear binary code with the distance d and the number of codewords at least m. (ial means the greatest integer, which is not greater than a). It is seen that, in contrast with the detection of all stuck-at faults, the detection of any fraction 1- $\beta$  of the total number of faults (even if this fraction is arbitrarily close to 1, but remains constant) requires asymptotically a number of test patterns which depends on  $\beta$  only, but does not depend on m and  $\beta$ .

Example 2. Let us estimate the minimum number of test patterns sufficient for detecting 99% of input stuck-at faults in almost all devices. Then  $\beta=0.01$  and, for k=1, (22) yields:  $N(F_{f_{i}}^{(St)}, m, k) \le 14$ . (If  $k \ge 7$ , then two test patterns are sufficient.)

6. Another advantage of the proposed approach - this time, one of the methodological nature - can be mentioned. Since from

the viewpoint of universal testing classes of circuit are

described probabilistically, this opens a way for applications of powerful mathematical techniques based on probability theory and theory of random processes (for sequential circuits) to testing problems. In particular, close relation between testing theory and information theory (including coding) can be already seen. (For example, universal tests for input bridging faults are based on optimal error - correcting codes - see [34]).

## 5.2. Limitations.

- 1. The major limitation of universal testing is that it becomes efficient only in the case when a broad spectrum of circuits is to be tested. This argument is applicable both for manufacturer and user testing. Indeed, if many copies of a few types of devices only are to be tested, there is a reason to invest into development of specific tests for each of the types, since a specific test may be shorter and may provide a sufficient coverage just for this particular type. Seemingly, the most justifiable application of universal tests is in the case of a user who has to test a large variety of devices which come in small numbers of copies. Moreover, there is a good reason to use universal tests as a first step in testing procedure, since with probability close to 1 they will detect faulty devices, thereby eliminating the necessity of further testing.

- 2. Though universal tests are good for almost all devices, there is always a danger that a particular device under test is a "goat". Since universal testing is based on probabilistic reasoning, it provides good results only in statistical sense and

cannot guarantee against individual failures.

3. The size of universal tests may appear to be substantially larger than that of specific tests. Naturally, that is the price for their universality. However, for many typical circuits (as we have seen it in the example of terminal faults in adders, subtractors, multipliers, decoders) the universal tests are not longer than specific ones.

Universal testing, by its nature, combines some feature of functional and random testing, filling the gap between them. Therefore, we shall compare in more details these two approaches with universal testing.

## 5.3. Universal vs. functional testing.

Functional testing requires complete knowledge of the functional description of the device under test, while universal testing based on general information only about the class of devices (such as number of input and output variables, some general features of circuit topology, etc.). Functional testing, being device-oriented, can provide shorter tests than the universal one, but has greater test generation complexity. It is usually very hard to estimate the fault coverage for functional tests. The fault coverage for universal tests is known in terms of probability that in a device chosen from a given class all (or a given fraction) of faults are detectable.

Let us illustrate the situation for the case of multiple input stuck-at faults. The problem of functional testing for this class of faults has been considered in [46,47]. It has been shown in [46] that, if the number of inputs m>5, a specific test

can be constructed for any such circuit which detects all input stuck-at faults and consist of not more than 2m-4 test patterns. There exists an example of a function which requires at least 2(m-r) tests patterns, where  $r\geq \log_2(m-r)$ . It follows from the results described in [33,34] that a universal test which consists of  $N=2m(\log_2 3+\delta)$  test patterns will detect all the input stuck-at faults in all possible devices, except for a fraction of  $2^{m\delta}$ . On the other hand, even for this simple class of faults functional test generation is much more complex than that for universal tests.

### 5.4. Universal vs. random testing.

At the first glance universal testing looks very similar to random testing. Indeed, both of them ignore specific features of the device under test and the performance of both types of tests can be characterized in terms of probability. However, this similarity is misleading, since there are essential differences between these two approaches which lead to different results as regards to the size of tests and their fault-detecting capability.

- 1. Universal tests are usually designed in a deterministic manner: where not only the test patterns, but also their order (in case of sequential circuits) may be essential. On the other hand, for random testing test patterns and their order are chosen randomly [5,17,18,19,20,21,22,23,24,25,48].

- 2. In contrast with random testing, universal tests are designed on the base of information about a <u>class</u> of circuits.

The class can be characterized by the numbers of input and output lines, feedback lines, memory cells, by the number of gates and/or internal lines, by characterization of the class inplemented functions, e.g., self-dual or symmetric functions, by features of circuit topology, such as path complexity, number of gate levels (e.g., PLA's), etc.

3. Universal tests are fault-oriented: they are designed for a specific class of faults and depend on this class, as we have seen in it on the example of single and multiple input stuck-at faults and input bridging faults at input lines. It was shown, for instance in [34], that one needs a universal test with two patterns only to detect all single input stuck-at faults in such devices as adders, subtractors, decoders, counters with parallel load while a random test would require more than log2 m test patterns. For the class of all input multiple bridging faults we need [34] N  $\sim$  log<sub>2</sub>m for universal tests (based on error-correcting codes with the distance depending on the multiplicity of faults), while a random test would require N > 210g2m to detect all single input bridging faults. Thus, as a rule, universal tests are substantailly shorter than random ones. However, in case of output faults universal test degenerate to random tests. As a matter of fact, the extent of universality is rather flexible and depends on the width of the class of circuits and the class of faults involved. If the classes are not specified, we come back to random testing, while a complete description of a device on functional or on gate level will lead to functional or gate-level testing, respectively. Thus, both device-specific and random testing may be considered as special limit cases of universal testing. The comparison of various types of testing is summarized in Table 2.

Table 2. Comparative characterization of various approaches to testing.

| Type of        | Input data  | Test        | Test size    | Fault       |

|----------------|-------------|-------------|--------------|-------------|

| testing        | for test    | generation  | necessary    | coverage    |

|                | generation  | complexity  | for a given  | for         |

|                | •           | !           | fault        | a given     |

|                | <u> </u>    | ļ           | COVETAGE     | test size   |

| 1. Gate-       | Gate-level  | Maximal     | - <b> </b>   |             |

| 1eve1          | description | (Optimal    | j            | i           |

|                | of the      | test        | Minimal      | Mazimal     |

|                | device      | generation  |              |             |

|                | under test: | is NP-hard) | Ť            |             |

|                | class of    | 1           | 1            |             |

|                | fault       | !           |              |             |

| <del>2</del> . | Functional  | ·¦          | Larger       | Lower than  |

| Functional     | description | [           | than for a   | for a gate- |

|                | of the      | İ           | gate-level   | level       |

|                | device      | Large       | test         | (often,     |

|                | under test: | 1           | 1            | difficult   |

|                | class of    | 1           |              | to          |

|                | faults      |             | 1            | estimate)   |

| 3.             | Description | Small (the  | Larger than  | High for    |

| Universal      | of a class  | same test   | for the      | almost      |

|                | of devices: | for the     | first two    | all devices |

|                | class of    | whole class | types.       | from a      |

|                | faults      | _           | (Depends on  | <u> </u>    |

|                | !           | for a given | the class of | class       |

|                | !           | set of      | devices and  |             |

|                | ]           | faults)     | the set of   |             |

|                | <br>        | }<br>       | ifaults)     | ļ.<br>1     |

| 4.             | Set of      |             | · <b> </b>   |             |

| Random         | possible    | <u>I</u>    | 1            |             |

|                | test        | Minimal     | Maximal      | Minimal     |

|                | patterns    | ļ           | [            |             |

|                | only        | Ţ           | ļ ļ          |             |

|                |             |             | !            |             |

|                |             |             | ·            |             |

Finally, we may conclude that universal testing suggests a viable alternative to other types of testing and expands the arsenal of tools for a testing engineer.

### REFERENCES

- [ 1] Ibarra, A.K. and Sahni, S., 'Polynomially Complete Fault Detection Problems', <u>IEEE Trans. on Computers</u>, C-24, March 1975, pp. 242-248.

- [2] Sahni, S. and Bhatt, A., 'The Complexity of Design Automation Problems', Proc. 17th Design Automation Conference, Minneapolis, MN, May 1980, pp. 402-411.

- [ 3] Broussard, M.E., 'Higher Yields, Lower Costs', Ibid., pp. 6-11.

- Chalkley, M.J., 'Trends in VLSI Testing', 1979 Test Conference, Oct. 23-25, 1979, pp. 3-6.

- [5] Breuer, M.A., and Friedman, A.D., 'Diagnosis and Reliable Design of Digital Systems', Computer Science Press, 1976.

- Roth, J.P., 'Diagnosis of Automata Failure: A Calculus and a Method', <u>IBM Journal of Research and Development</u>, Vol. 10, July 1966, pp. 278-291.

- Sellers, F.F., Hsiao, M.Y., and Bearnson, C.L., 'Analyzing Errors with the Boolean Difference', <u>IEEE</u>

Trans. on Computers, C-17, July 1968, pp. 676-683.

- [8] Goel, P., 'Test Generation Cost Analysis and Projections', <u>17th Design Automation Conference Proceedings</u>, Minneapolis, MN, June 1980, pp. 77-84

- Thatte, S.M., and Abraham, J.A., 'Test Generation for Microprocessors', <u>IEEE Trans. On Computers</u>, Vol. C-29,N6, June 1980, pp. 423-441.

- [10] Abraham, J.A., and Parker, R.P., 'Practical Microprocessor Testing: Open Loop and Closed Loop Approaches', FTCS 1981.

- Akers, Sheldon B., 'Functional Testing with Binary Decision Diagrams', The 8th Annual International Conference on Fault Tolerant Computing, Toulouse, France, June 1978.

- [12] Karpovsky, M.G., 'Error Detection in Digital Devices and Computer Programs with the Aid of Linear Recurrent Equations over Finite Commutative Groups', <u>IEEE Trans.on Computers</u>, C-26, N3, 1377, pp. 208-219.

- [13] Karpovsky, M.G., and Trachtenberg, E.A., 'Linear Checking Equations and Error-Correcting Capability of Holland, pp. 619-624, 1977.

- [14] Goel, N., and Karpovsky, M.G., 'Functional Testing of Computer Hardware Based on Minimizaton of Magnitude of Undetected Errors', <u>IEEE Proc.</u>, Vol. 129, Sept. 1982, pp. 169-181.

- Akers, S.B., 'Functional Testing with Binary Decision Diagrams', The 8th Int. Symposium on Fault-Tolerant Computing, Toulouse, France 1978, pp. 75-82.

- Shedletsky, J.J., 'Random Testing: Practicality vs. verified effectivness', The 7th Annual Intern. CA, June 1977, pp. 175-179.

- Rault, J.C., 'A Graph Theoretical and Probabilistic Approach to the Fault Detection of Digital Circuits', International Symposium on Fault-Tolerant Computing, March 1971, pp. 16-29.

- David, R., and Thevenod-Fosse, P., 'Minimal Detecting Transition Sequences: Application to Random Testing', 518.

- Agrawal, V.D., and Agrawal, P., 'An Automatic Test Generation System for ILLIAC-IV Logic Boards', IEEE Trans. on Computers, Vol. C-21, pp. 1015-1017, Sept. 1972.

- Agrawal P., and Agrawal, V.D., 'Probabilistic Analysis of Randon Test Generation Method for Irreductant Logic Networks', <u>IEEE Trans. on Computers</u>, Vol. C-24, pp. 681-

- Agrawal, P., and Agrawal V.D., 'On Improving the Efficiency of Monte Carlo Test Generation', Int. Symposium on Fault-Tolerant Computing, Paris, France, pp. 205-208, June 1975.

- Bostin, D., Girard, E., Rault, J.C., and Tullone, R., 'Probabilistic Test Generation Methods', Int. Symposium on Fault-Tolerant Computing, Palo Alto, CA, p. 171, June 1973.

- [23] Savir, J., Ditlow, G., and Bardell P.H., 'Random Pattern Testability', <u>International Symposium on Fault-Tolerant Computing</u>, June 1983, Milano, Italy.

- [24] Thevenod, P., and David, R., 'Random Testing of Control Section of a Microprocessor', <u>International Symposium on Fault-Tolerant Computing</u>, June 1983, Milano, Italy.

- [25] Thevenod-Fosse, P., and, David, R., 'A Method to Analyze Random Testing of Sequential Circuits', <u>Digital</u>

<u>Processes</u>, Vol. 4, pp. 313-332, 1978.

- [26] McCluskey, E.J., Bozorgui-Nesbat, S., 'Design for Autonomous Test', <u>IEEE Trans. on Computers</u>, V. C-30, pp. 866-875.

- [27] Savir, J., 'Syndrome-Testable Design of Combinational Circuits', IEEE Trans. on Computers, C-29, No 6, June 1980, pp. 442-450.

- [28] Barzilai, Z., Coppersmith, D., and Rosenberg, A., 'Exhaustive Bit Pattern Generation in Discontiguous Positions, with Applications to VLSI Self-testing', IBM Research Report, RC-8750, March 1981.

- [29] Tang, T.D., Chen, C.L., 'Logic Test Pattern Generation using Linear Codes', Proc. of 13th International Fault-Tolerant Computing Symposium, Milano, Italy, June 1983, pp. 222-226.

- [30] Tang, T.D. and Woo, L.S., 'Exhaustive Test Pattern Generation with Constant Weight Vectors', <u>IBM Research Report</u>, RC-9442, June 1982.

- [31] Karpovsky, M.G., 'Universal Tests for Detection of Input/Output Stuck-at and Bridging Faults', <u>IEEE Trans</u>.

on Computers, Nov. 1983.

- [32] Karpovsky, M.G., 'Universal Tests Detecting Input/Output Faults in Almost All Devices', Proc. of 1982 Int. Test Conference, Cherry Hill, NJ, Nov. 1982.

- [33] Karpovsky, M., and Levitin, L., 'Error Detection in Combinational Networks by Use of Codes Based on Hadamard Matrices', 1983 IEEE Inter. Symp. on Information Theory, St. Jovite, Quebec, Canada, 1983.

- [34] Karpovsky, M.G., and Levitin, L., 'Detection and Identification of Input/Output Stuck-at and Bridging Faults in Combinational, and Sequential VLSI Networks by Universal Tests', to appear in Integration, The VLSI Journal, 1983.

- [35] Shannon, C.E., and Weaver, W., 'The Mathematical Theory of Communication', Univ. of Illinois Press, Urbana, IL, 1949.

- [36] Levitin, L. 'Information Content of an Image, Applications of Holography and Optical Data Processing', Pergamon Press, 1977.

- [37] Levitin, L., 'A Thermodynamic Characterization of Ideal Physical Information Channels', Journal of Information and Optimization Sciences, V. 2, No. 3, September 1981.

- Levitin, L., 'Physical Limitations of Rate, Depth and Minimum Energy in Information Processing', <u>International</u> Journal of Theoretical Physics, V. 21, No. 2/3, 1982.

- [39] Shmukler, Yu., 'Unidimensional and Bidimensional Gur Games', Automation and Remote Control, No. 10, 1970, p.1634.

- [40] Shmukler, Yu., 'Ballot Problem with a Random Error', DAN SSSR, v. 196, No. 4, 1971, p. 789.

- Rosonoer, L.I., 'Random Logical Nets, I, II, and III', <u>Automation and Remote Control</u>, No. 5, pp. 773-781, No. 6, pp. 922-931, No. 7, pp.1130-1139, 1969.

- Fujiwara, H., Kinoshita, K., and Ozaki, H., 'Universal Test Sets for Programmable Logic Arrays', in Dig. 10th Inter. Symp. on Fault-tolerant Computing, Kyoto, Japan, June 1980, pp. 137-142.

- Fujiwara, H., Kinoshita, K., 'A Design of Programmable Logic Arrays with Universal Tests', <u>IEEE Trans. on Circuits and Systems</u>, V. CAS-28, No. 11, pp. 1027-1032, Nov. 1981.

- Lupanov, O.B., 'On the Possibilities of Synthesis of Networks from Different Types of Elements', <u>Dok1. Akad.</u>

Nauk, USSR, 103, (1955), pp. 561-563.

- [45] MacWillilams, F.J. and Sloane, N.J.A., The Theory of Error-Correcting Codes, North Holland, 1977.

- Weiss, C.D., 'Bounds on the Length of Terminal Stuck-Fault Tests', <u>IEEE Trans on Computers</u>, C-21, 1972, pp.305-309.

- Kuhl T.G., and Reddy, S.M., 'On Detection of Terminal Stuck-Faults', <u>IEEE Trans. on Computers</u>, C-27, May 1978, pp. 467-469.

- Huary, H., and Breuer, M.A., 'Analysis of Detectability of Faults by Random Patterns in a Special Class of NAND Networks', Computer and Elect. Engr., Vol. 1, pp. 77-84, March 1975.