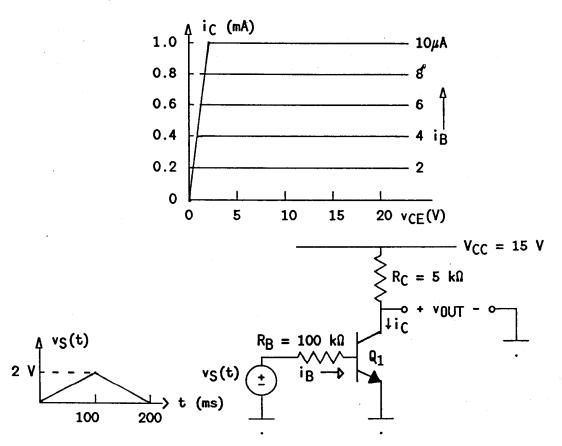

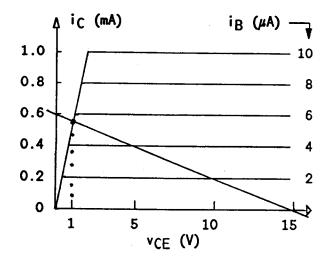

A bipolar junction transistor (BJT) has the v-i characteristics shown below. The device is connected to a simple inverter circuit whose input consists of a triangular voltage pulse  $v_S(t)$  that rises from zero to 2 V in 100 ms, then falls to zero after another 100 ms. Find the resulting output voltage  $v_{OUT}(t)$ . Assume that  $V_f = 0.7$  V for the base-emitter junction of  $Q_1$ .

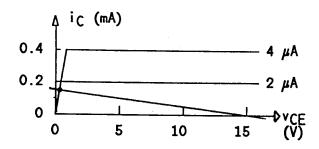

- 6.2 Repeat Prob 6.1 if  $R_C$  is changed from 5 k $\Omega$  to 25 k $\Omega$ .

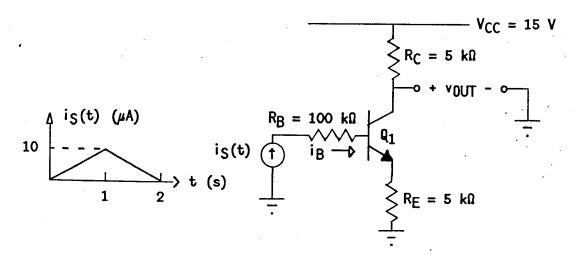

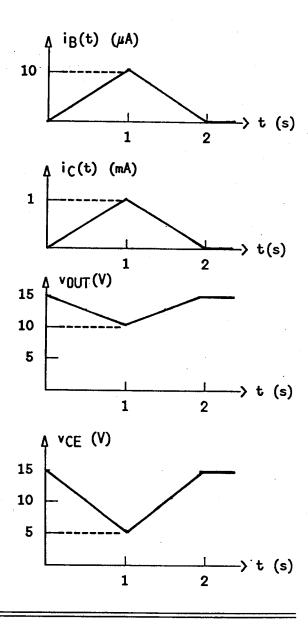

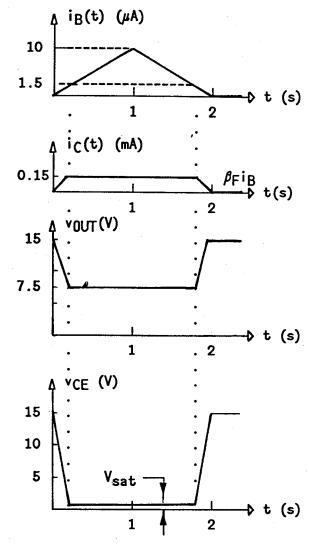

- 6.3 A bipolar junction transistor (BJT) has the v-i characteristics shown in Prob. 6.1. The device is connected to the circuit shown below. The input consists of a triangular current pulse is(t) that rises from zero to 10  $\mu$ A in 1 s, then falls to zero after another 1 s. Find the output voltage volt(t). Assume that VBE = Vf = 0.7 V when iB > 0.

- Repeat Prob 6.3 if R<sub>C</sub> and R<sub>E</sub> are both changed from 5 k $\Omega$  to 50 k $\Omega$ .

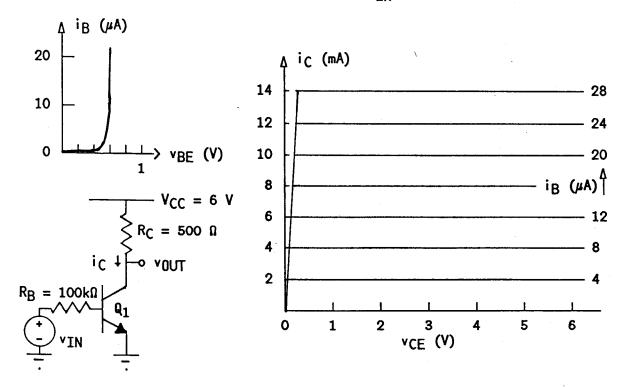

- An NPN BJT with the v-i characteristics shown below is connected in a basic inverter circuit with resistive pullup load. Use the graphical technique to plot the voltage transfer characteristic of the inverter over the input range -2 V  $\langle$  vIN  $\langle$  5 V.

- 6.6 Consider the BJT inverter circuit of Prob. 6.5. The BJT has the v-i characteristics shown above.

- a) What is the value of  $\beta_{\rm F}$  for this BJT?

- b) For  $v_{IN} = 2.5 \text{ V}$ , find ic and  $v_{OUT}$  using analytical methods.

- c) The BJT is now replaced by a device with twice the value of  $\beta_F$ . What happens to the values of ic and  $v_{OUT}$  computed in part b)?

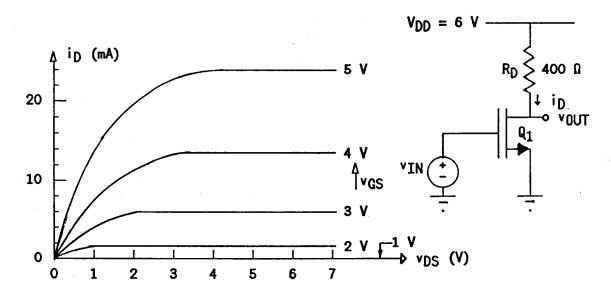

6.11 An enhancement-mode n-channel MOSFET having the v-i characteristics shown below is connected in a basic inverter circuit with resistive pullup load, as indicated. Use the graphical technique to plot the voltage transfer characteristic of the inverter.

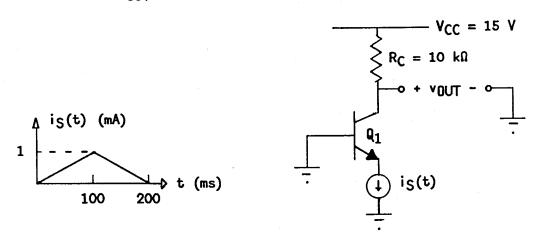

6.12 A bipolar junction transistor (BJT) has the v-i characteristics given in Prob. 6.1. The device is connected to the circuit shown below. The input consists of a triangular current pulse is(t) that rises from zero to 1 mA in 100 ms, then falls to zero after another 100 ms. This current is drawn from the emitter terminal of  $Q_1$ , which is connected in the tracking configuration. Find the output voltage  $v_{OUT}(t)$ .

- 6.13 Repeat Prob. 6.12 if RC is changed from 10 k $\Omega$  to 20 k $\Omega$ .

- 6.14 Design a new version of the tracking circuit of Prob. 6.12 that has as its input a voltage source  $v_S(t)$ . The  $v_S$  input source should directly produce an equivalent tracked input current is.

- 6.7 Consider the BJT inverter circuit of Prob. 6.5. The BJT has the v-i characteristics shown. Use analytical methods to find the slope dvout/dvin when the BJT operates in its active (constant-current) region.

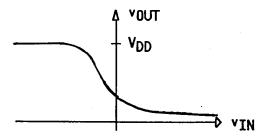

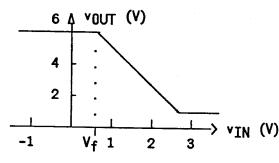

- 6.8 Using identical n-channel MOSFETs only, design a circuit for which the voltage transfer characteristic has the basic form shown below.

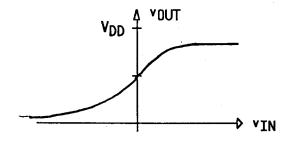

6.9 Using only n-channel and p-channel depletion-mode MOSFETs, design a CMOS circuit whose voltage transfer characteristic has the basic form shown below. Note that  $v_{OUT}$  is equal to  $V_{DD}/2$  at  $v_{IN}=0$ . The circuit drives a load resistance  $R_{L}$ .

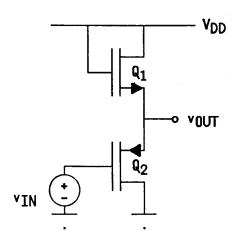

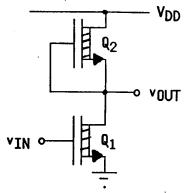

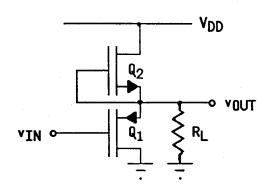

6.10 Determine the general form of the voltage transfer characteristic of the NMOS/PMOS (CMOS) circuit shown below

6.15 Find the transfer characteristic of the JFET circuit shown below. The devices have the same values of  $\mbox{Vp}$  and  $\mbox{I}_{DSS}$ .

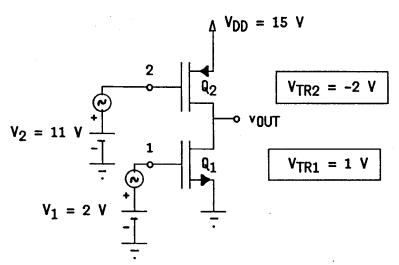

- 6.16 In the CMOS circuit shown below, nodes 1 and 2 are connected to signal sources that contain dc components of 2 V and 11 V, respectively.

- a) For what range of  $v_{\mbox{\scriptsize OUT}}$  is  $\mbox{\bf Q}_1$  in the constant-current region?

- b) For what range of  $v_{OUT}$  is  $Q_2$  in the constant-current region?

6.17 Consider the CMOS circuit described in Prob 6.16. Suppose that the two inputs are connected together and driven by a common input source vIN. Make a qualitative sketch of the resulting vIN-vour transfer characteristic.

Solutions

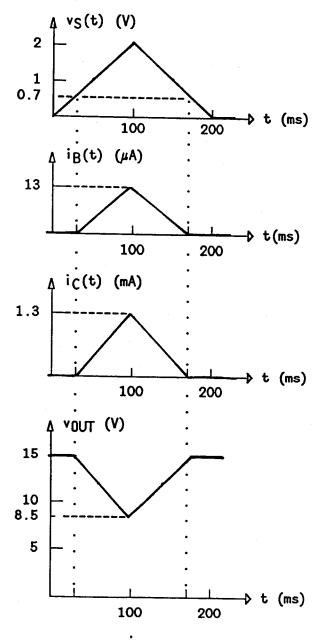

Application of KVL to the output loop of this circuit yields  $v_{OUT} = V_{CC} - i_{CRC}$ . The next step involves determining ic as a function of  $v_{S}$ . For input voltages  $v_{S} < V_{f}$ , the basemitter junction of  $Q_{1}$  will not be forward biased, and the transistor will be in cutoff. Under cutoff conditions, both iB and ic will be zero and  $v_{OUT}$  will equal  $V_{CC}$ .

For values of  $v_S$  larger than  $V_f$ , application of KVL to the input loop of the circuit yields  $i_B = (v_S - V_f)/R_B$ . At the peak value of  $v_S$ ,  $i_B$  will be equal to  $(2 \ V - 0.7 \ V)/(100 \ k\Omega) = 13 \ \mu A$ . When  $v_S$  again falls below 0.7 V,  $i_B$  will fall back to zero.

For vs > V<sub>f</sub>, is will rise and fall linearly with vs. An inspection of the BJT v-i characteristics reveals that ic/is =  $\beta_F$  = 100 in the BJT's constant-current region. As long as the BJT does not reach saturation, ic will thus increase linearly with vs for vs > V<sub>f</sub> and will be equal to ic =  $\beta_F$ (vs - V<sub>f</sub>)/R<sub>B</sub>. At the peak value of

vs, ic will be equal to  $100(13~\mu\text{A}) = 1.3~\text{mA}$ . For this value of ic, vout becomes  $V_{CC}$  - icR<sub>C</sub> = 15 V - (1.3 mA)(5 kΩ) = 8.5 V. This value of vout, which is also the value of vcE for the BJT, is well in excess of  $V_{\text{sat}}$ , indicating that the BJT does not reach saturation, even at the peak value of vs. Plots of vs(t), ig(t), ic(t), and vout(t) are shown below.

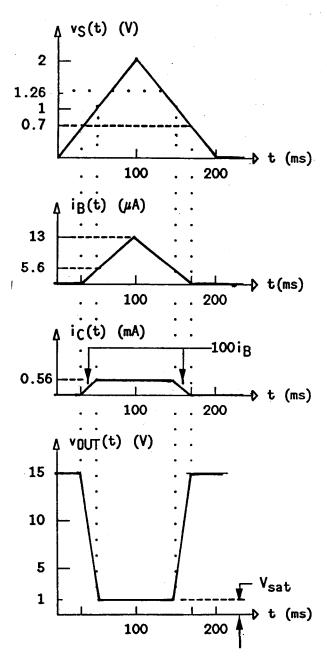

6.2 The base-emitter loop of the modified circuit is identical to that of the original, so that is again reaches a peak of 13  $\mu$ A when  $v_S =$ In this case, however, the larger value of RC causes a larger proportional drop in vout for the same change in ic. The BJT reaches its saturation point  $v_{CE} = V_{sat}$ before the peak of vs is reached. The exact values of ic and voe at saturation can be found by plotting the load line of  $V_{CC}$  and  $R_C$  over the v-i characteristics of the BJT:

With R<sub>C</sub> = 25 k $\Omega$ , the intercepts of the load line are V<sub>CC</sub> = 15 V (open circuit voltage of the Thevenin circuit formed by V<sub>CC</sub> and R<sub>C</sub>) and V<sub>CC</sub>/R<sub>C</sub> = 0.6 mA (short circuit current of the Thevenin circuit).

As is evident from the figure, the BJT reaches saturation when  $v_{CE} \simeq 1 \text{ V}$  and  $i_{C} = 0.56 \text{ mA}$ . This latter value can be confirmed by applying KVL to the output loop of the circuit with  $v_{CE} = V_{sat}$ , yielding

$$i_C = \frac{V_{CC} - V_{sat}}{R_C} = \frac{15V - 1V}{25 \text{ k}\Omega} = 0.56 \text{ mA}$$

The ig value corresponding to arrival at this saturation point is given by

$(0.56 \text{ mA})/100 = 5.6 \mu\text{A}$ , for which v<sub>IN</sub> = 1.26 V.

For a given vg, the value of iB will be the same as that found in Prob 6.1. For the modified circuit, ic will rise with iB as  $\beta$ FiB until the BJT saturates. For larger values of vg, iB will increase but ic will remain constant. Similarly, vout will fall linearly with rising vg and iB until it reaches the value  $V_{sat}$  and will remain constant thereafter. Plots of vg(t), iB(t), iC(t), and the resulting vout(t) are shown to the right.

This space intentionally left blank

6.3 The value of V<sub>f</sub> for the baseemitter junction of the BJT is irrelevant to this problem. The is(t) forces its current source current into the base of Q1 regardless of the value of vBE. voltage across the is source adjusts itself to be whatever value of vBE is required for the established ig.

For a given instantaneous value of is, the value of ic will be equal to  $\beta_{\text{F}}$  is provided that  $Q_1$  does not saturate. The resulting output voltage becomes  $v_{\text{OUT}} = V_{\text{CC}} - i_{\text{C}}R_{\text{C}}$ , where  $v_{\text{CE}} = V_{\text{CC}} - i_{\text{C}}R_{\text{C}} - i_{\text{E}}R_{\text{E}}$ . Since  $\beta_{\text{F}} >> 1$  it follows that  $i_{\text{E}} \simeq i_{\text{C}}$ , so that

vCE  $\cong$  VCC - iC(RC + RE) Knowledge of vCE is needed to determine when Q<sub>1</sub> goes into saturation.

At the peak value of is, ic will equal  $\beta_{\text{FiS}} = 100(10 \ \mu\text{A}) = 1 \ \text{mA}$ , so that  $v_{\text{OUT}} = 15 \ \text{V} - (1 \ \text{mA})(5 \ \text{k}\Omega) = 10 \ \text{V}$ . Note that  $v_{\text{CE}} = 15 \ \text{V} - (1 \ \text{mA}) \times (5 \ \text{k}\Omega + 5 \ \text{k}\Omega) = 5 \ \text{V}$  at the peak of is. This vcE voltage is clearly above  $V_{\text{Sat}}$ , indicating that the BJT is never driven into saturation.

Plots of iB = iS, iC,  $v_{OUT}$ , and  $v_{CE}$  versus time are shown to the right. Note that iC,  $v_{OUT}$ , and  $v_{CE}$  all change linearly with iS.

This space intentionally left blank

iB will again be equal to ig. In this case, however, the larger values of RC and RE will cause a larger proportional drop in vout and vCE for the same increase in ic. Thus Q1 will reach its saturation point, with vCE = Vsat, before the peak of ig is reached. The exact values of ic and vCE at saturation can be found by plotting the load line of the voltage VCC and total resistance (RC + RE) over the BJT v-i characteristics:

With  $R_C = R_E = 50 \text{ k}\Omega$ , the intercepts of the load line are  $V_{CC} = 15 \text{ V}$  (open circuit voltage of the Thevenin circuit formed by  $V_{CC}$ ,  $R_C$ , and  $R_E$ ) and  $V_{CC}/(R_C + R_E) = 0.15 \text{ mA}$  (short circuit current of the Thevenin circuit). As is evident from the figure, the BJT reaches saturation when  $v_{CE} \cong 0.2 \text{ V}$  and  $i_C \cong 0.15 \text{ mA}$ . This latter value can be confirmed by applying KVL to the output loop of the circuit with  $v_{CE} = V_{sat}$ , yielding

$$i_{C-sat} = \frac{V_{CC} - V_{sat}}{R_C + R_E}$$

$$= \frac{15 \text{ V} - 0.2 \text{ V}}{100 \text{ k}\Omega} = 0.148 \text{ mA} \approx 0.15 \text{ mA}$$

Note that ic will rise with iB up to the value 0.15  $\mu$ A, at which point the BJT will saturate; ic will remain constant for higher values of iB. Similarly, vout and vcE will fall linearly with iB until vcE reaches its value of  $V_{sat}$ , at which point vout =  $V_{CC}$  -  $i_{C-sat}R_{C}$

= 15 V -  $(0.15 \text{ mA})(50 \text{ k}\Omega)$  = 7.5 V Plots of  $v_S(t)$ ,  $i_B(t)$ ,  $i_C(t)$ , and the resulting  $v_{OUT}(t)$  are shown below.

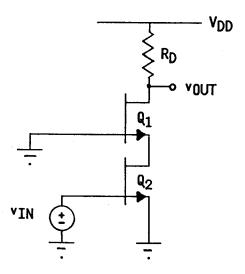

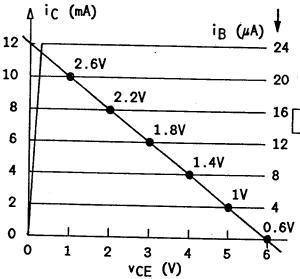

6.5 The collector and emitter

terminals of the BJT are connected directly to the Thevenin circuit formed by  $V_{CC}$  and  $R_C$ . The load line representing these resistive elements can be plotted directly over the v-i characteristics of the BJT, as shown below. For this load line,  $V_{Th} = 6V$  and  $V_{Th}/R_{Th} = (6 \text{ V})/(500 \Omega) = 12 \text{ mA}$ .

The operating point of the BJT will be determined by the value of ig. In this case, ig can be found by plotting the load line of  $v_{\mbox{\footnotesize{IN}}}$  and  $R_{\mbox{\footnotesize{B}}}$  over the given base-emitter v-i characteristics. Alternatively, this curve can be used to estimate the value of Vf for the base-emitter junction. KVL can then be used to find ip as a function of v<sub>IN</sub>. Using the latter method yields  $i_B = (v_{IN} - V_f)/R_B$ where, from the figure,  $V_f \simeq 0.6 \text{ V}$ . Several operating points, labeled by the v<sub>IN</sub> value that yields the corresponding in, are indicated in the figure above. These points can be used to plot the transfer characteristic of the inverter:

Note that  $v_{OUT}$  remains fixed at  $V_{CC}$  until  $v_{IN}$  exceeds the BJT "threshold" voltage  $V_f$ . Similarly, for values of

VIN greater than about 2.8 V (i.e., iB > 22  $\mu$ A), the BJT goes into saturation with v<sub>OUT</sub>  $\simeq$  0.25 V.

by finding the ratio of ic to iB at several points in the constant-current region. The v-i curves are evenly spaced, so the value of  $\beta_F$  can be computed anywhere. Along the constant-current portion of the iB = 24  $\mu$ A curve, for example, iC = 12 mA, so that  $\beta_F$  = (12 mA)/(24  $\mu$ A) = 500.

- b) From the base-emitter v-i characteristic, we note that  $V_f \simeq 0.6 \text{ V}$ . For a given vIN, the value of iB can be found by applying KVL to the input loop of the circuit, yielding in =  $(v_{IN} - V_f)/R_B$ . Thus, for  $v_{TN} = 2.5$ V,  $i_B = (2.5V - 0.6V)/100k\Omega = 19 \mu A$ . For a  $\beta_F$  of 500, ic becomes  $\beta_{FiB} =$  $500(19 \mu A) = 9.5 \text{ mA}$ . Finally, the value of vout can be computed by applying KVL to the output loop of the circuit, yielding  $v_{OUT} = V_{CC}$   $i_{C}R_{C} = 6 \text{ V} - (9.5 \text{ mA})(500 \Omega) = 1.25$ V. This  $v_{OUT}$  is well in excess of the BJT's saturation voltage V<sub>sat</sub>, indicating that the transistor is not driven to saturation by vIN.

- c) If  $\beta_{\rm F}$  is doubled, the collector current ic will attempt to increase to the value  $1000(19~\mu{\rm A})=19~{\rm mA}$ . If reached, this ic value would result in a voltage drop across R<sub>C</sub> of (19 mA)(500  $\Omega$ ) = 9.5 V. This unattainable voltage value exceeds the available power supply voltage V<sub>CC</sub> = 6 V. It would also would require that volt somehow drop to a negative value, which it cannot do. We thus conclude that the BJT is driven to

saturation with  $v_{OUT} = V_{sat} \approx 0.25 \text{ V}$ (see Prob 6.5) and  $i_{C-sat} = V_{sat} = 0.25 \text{ V}$

$$\frac{V_{CC} - V_{sat}}{R_C} = \frac{6 \text{ V} - 0.25}{500 \text{ }\Omega} = 11.5 \text{ mA}$$

Note that ic/iB  $\neq \beta_F$  in this case, but the value of iB, which is determined by KVL taken around the input loop, is still equal to 19  $\mu$ A.

The value of iB for this circuit is given by iB =  $(v_{IN} - V_f)/R_B$  (see Prob. 6.5). If the BJT operates in the constant current region, then iC will equal  $\beta_{FiB}$ . Meanwhile,  $v_{OUT} = V_{CC} - i_{CRC} = V_{CC} - \beta_{FiB}R_C$ , or  $v_{OUT} = V_{CC} - \frac{\beta_{F}(v_{IN} - V_f)R_C}{R_B}$

Taking the slope  $dv_{OUT}/dv_{IN}$  of this equation yields the voltage "gain" of the circuit, which is equal to  $dv_{OUT}/dv_{IN} = -\beta_F R_C/R_B$ .

that of an inverter. The circuit turns on (current begins to flow through the pull-up device) for negative values of vIN. The input device of the inverter must therefore be a depletion-mode MOSFET. Since all devices are to be identical, the upper device must also be a depletion mode MOSFET:

Note that  $Q_2$  has its gate connected to its source, so that  $v_{GS2}=0$ . This connection allows  $i_{D2}$  to be nonzero for all values of  $v_{DS2}$ . The exact value of  $v_{DS2}$  is determined by the  $v_{GS}=0$  v-i characteristic of  $Q_2$ . The current through  $Q_2$  is set by  $Q_1$ .

when vIN is negative. The output is high (i.e., the input device is in cutoff) for more positive values of vIN. This characteristic can be obtained if a p-channel transistor and n-channel transistor are connected as shown below:

A depletion-mode p-channel device has a positive  $V_{TR}$ , yielding a positive turn-on value of  $v_{IN}$ . This condition is compatible with the indicated transfer characteristic.

With a p-channel device used as the input transistor, the circuit will

take on complementary form if an n-channel MOSFET is used for the pullup load. The gate of  $\mathbb{Q}_2$  is connected to its source, causing  $\mathbb{Q}_2$  to operate on its vgs=0 v-i characteristic. This connection allows  $\mathbb{Q}_2$  to conduct and to pull vout up toward VDD when  $\mathbb{Q}_1$  goes into cutoff.

6.10 For this circuit, the n-channel pullup device Q<sub>1</sub>, for which v<sub>GS1</sub> = v<sub>DS1</sub>, obeys the v-i equation

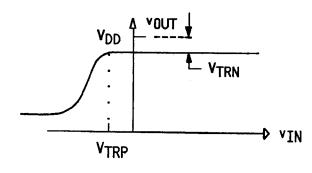

$i_D = K(V_{DD} - v_{OUT} - V_{TRN})^2$ . Note that  $Q_1$ , with a positive  $V_{TR}$ , automatically operates in the constant-current region, since condition vDS1 > vGS1 - VTRN will always be met. When vIN is low, the p-channel input device Q2 is driven conduction, pulling current through  $Q_1$  and causing  $v_{OUT}$  to fall to a small value.  $\mathbb{Q}_2$  will conduct as long as  $v_{IN}$  is less than  $V_{TRP}$ . When VIN is high, Q2 enters the cutoff It would seem that vour state. should rise to the value VDD, but this output can be obtained only if the vnin terminal drives no load. If the slightest load current is drawn from the  $v_{OUT}$  terminal, a  $v_{GS1}$  of VTRN is required, causing vout to fall to the value  $V_{

m DD}$  -  $V_{

m TRN}$ . The transfer characteristic thus has the form shown below.

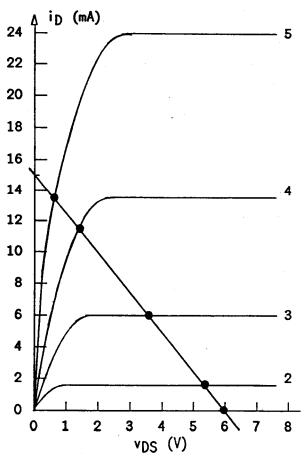

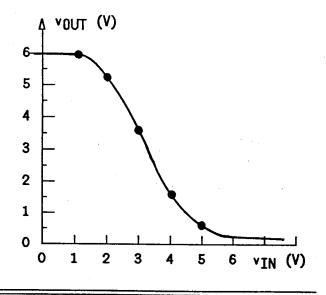

The drain and source terminals 6.11 of the MOSFET are connected directly to the Thevenin circuit formed by  $V_{DD}$ and Rp. The load line representing these Thevenin elements can be plotted directly over the v-i characteristic of the MOSFET, as shown below. In this case,  $V_{Th} = 6 V$  and  $V_{Th}/R_{Th} =$  $(6 \text{ V})/(400 \Omega) = 15 \text{ mA}.$ representative operating points, indicated in the figure, are used to construct the accompanying transfer characteristic. Note that vour remains fixed at  $V_{DD}$  until  $v_{IN}$  exceeds the MOSFET threshold voltage  $V_{TR} =$ For vin greater than about 3.5 V, the MOSFET enters the triode region of operation.

6.12 For a BJT in the active (constant-current) region, ic =  $\beta_{\text{FiR}}$  and  $i_E = (\beta_F + 1)i_B$ . If  $\beta_{F} >> 1$  , then i<sub>E</sub> ≃ i<sub>C</sub>. An examination of any one of the horizontal lines on the set of v-i characteristics shows this BJT to have a  $\beta_F = i_C/i_B$  of about 100. Clearly,  $\beta_F \gg 1$  for this transistor. The input current source directly sets if (i.e., ic) to the value is. Thus  $v_{OUT} = V_{CC} - i_SR_C$ . For  $i_S = 0$ ,  $v_{OUT} = V_{CC} = 15 \text{ V}$ . For  $i_S = 1 \text{ mA}$ (peak value of is),  $v_{\text{OUT}} = 15 \text{ V} - (1 \text{ m})$ mA) (10 k $\Omega$ ) = 5 V. The value of v<sub> $\Omega$ </sub> $\Gamma$  $\Gamma$ will change linearly with is for values of is between these two

versus time for the indicated is is

extreme limits.

shown below.

6.13 This problem is similar to Prob. 6.12. In this case, however, the voltage drop across R<sub>C</sub>, equal to (essentially equivalent icRc isRc), appears to exceed Vcc as is heads toward its peak value of 1 mA. In reality, the BJT will be driven out of its constant-current region and into saturation when is reaches the value 0.78 mA. This value can be computed by assuming V<sub>sat</sub> ≈ 0.2 V and by noting that the emitter of  $Q_1$  is held at -V<sub>f</sub> ≃ -0.7V as long as current flows through the baseemitter junction. Q<sub>1</sub> will reach saturation when  $v_{CE} = V_{sat}$ , i.e. when  $v_{OUT} = -V_f + V_{sat} = -0.5 V$ . Given that  $v_{OUT} = V_{CC} - i_SR_C$  for values of is up to the saturation value of is point, the limiting becomes  $[15 \text{ V} - (-0.5 \text{ V})]/(20 \text{ k}\Omega) =$ 0.78 mA. For larger values of is, VOLT will remain fixed at -0.5 V. Further increases in is will flow directly via the base-emitter junction of the BJT without extracting an

A plot of voin

additional current component from ic. Note that under saturation conditions, ic  $\neq \beta_{\text{FiB}}$ .

It is also interesting to note the nature of the is current source. If truly ideal, this source will adjust the voltage across its terminals to meet the constraints of its load. Thus, the top terminal of the is source will be held at the value -Vf relative to ground for all values of is greater than zero.

Here is a plot of vour versus is:

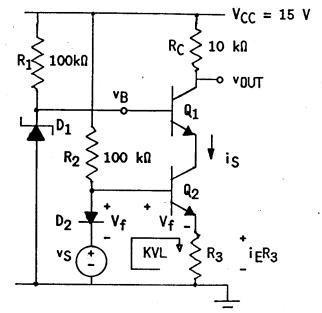

6.14 Many designs will accomplish the desired task. Here is one design that utilizes a second BJT:

In this circuit, the large resistance  $R_2$  forward-biases  $D_2$  by forcing a small current through the diode and into the  $v_S$  source. The voltage drop across  $D_2$ , which is approximately equal to  $V_f$ , is used to overcome the base-emitter voltage drop of  $\mathbb{Q}_2$ . Applying KVL to the base loop of  $\mathbb{Q}_2$  yields

from

$$D_2$$

from  $Q_2$

$$-v_S - V_f + V_f + i_E R_3 = 0$$

==>  $i_E = v_S/R_3$ . For large  $\beta_F$ ,  $i_S \simeq i_E = v_S/R_3$ .

The purpose of the zener  $D_1$  is to provide a voltage above ground for the base terminal of  $Q_1$ .  $D_1$  is forced into its reverse-breakdown region by  $R_1$ , so that  $v_B = V_{ZK}$ . Without the zener in place, the base of  $Q_1$  would be held at ground, forcing the voltage of the emitter of  $Q_1$  to the value  $-V_f$ . This condition would also require that the collector of  $Q_2$  be held at  $-V_f$  relative to ground. Since ground (0 V) is the lowest voltage in the circuit, this

condition cannot be met. Including the zener  $D_1$  eliminates the problem.

Recall that Vp of the n-channel JFETs has a negative value.

6.15 | The first step is the

computation of the current  $i_{D2}$  as a function of  $v_{IN}$ . An examination of  $Q_2$  reveals that  $v_{GS2} = v_{IN}$ . If  $Q_2$  operates in its constant-current region, then

$$i_{D2} = (I_{DSS}/V_P^2)(v_{GS2} - V_P)^2$$

=  $K(v_{IN} - V_P)^2$

where the equivalent JFET parameter  $K = I_{DSS}/V_P^2$  has been substituted.

For gate currents into the JFETs of zero, it follows that  $i_{D1} = i_{D2}$ . If  $Q_2$  operates in its constant-current region, it follows that

$$v_{OUT} = V_{CC} - i_{D2}R_{D}$$

$$= V_{CC} - KR_{D}(v_{IN} - V_{P})^{2}$$

The above analysis assumes both JFETs to operate in the constant current region. Device  $Q_2$  will do so for

Since  $v_{DS2} = -v_{GS1}$ , this condition becomes

If  $Q_1$  also operates in the constant-current region, then  $v_{QS1}$  will equal  $v_{QS2}$  for matched devices, as noted above. Under such conditions, the constant-current condition on  $Q_2$  can be expressed as

With  $v_{GS2} = v_{IN}$ , this condition becomes  $v_{IN} < V_P/2$ .

The above analysis assumes  $\mathbb{Q}_1$  to operate in the constant-current region. It will do so if

Or

stant current region if  $v_{DS1} > v_{GS1} - v_{TR1}$ . For this circuit,  $v_{DS1} = v_{OUT}$ , so that the above condition becomes  $v_{OUT} > v_{GS1} - v_{TR1} = 2 \ V - 1 \ V = 1 \ V$ . In the above equation, the bias value of  $v_1$  has been substituted for  $v_{GS1}$ .

b) Similarly,  $Q_2$ , the p-channel device, will operate in the constant-current region for  $v_{DS2} < v_{GS2} - V_{TR2}$ . The bias value of  $v_{GS2}$  is equal to  $V_2$  -  $V_{DD}$ , and  $v_{DS2}$  =  $v_{OUT}$  -  $V_{DD}$ . The constant-current region condition thus becomes

$v_{OUT} - V_{DD} < V_2 - V_{DD} - V_{TR2}$ , or  $v_{OUT} < V_2 - V_{TR2} = 11V - (-2V) = 13 V$ Both devices will operate in the constant-current region for

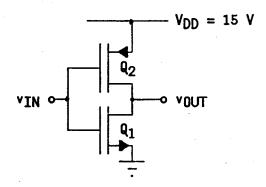

6.17 Here is a diagram of the circuit described in the problem:

For  $v_{IN}$  >  $v_{TRN}$ ,  $v_{GS1}$  will exceed the threshold voltage of  $Q_1$ , causing the n-channel device to conduct and  $v_{OUT}$  to be forced toward ground. Over this region of operation,  $Q_2$  will function as the pullup load to  $Q_1$ .

For  $v_{IN} - V_{DD} < V_{TRP}$ ,  $\mathbb{Q}_2$  will conduct, forcing  $v_{0UT}$  toward  $V_{DD}$ . Note that  $V_{TRP}$  has a negative value. Over this region of operation,  $\mathbb{Q}_1$  will function as the pulldown load to  $\mathbb{Q}_2$ . Here is a qualitative sketch of the resulting transfer characteristic: